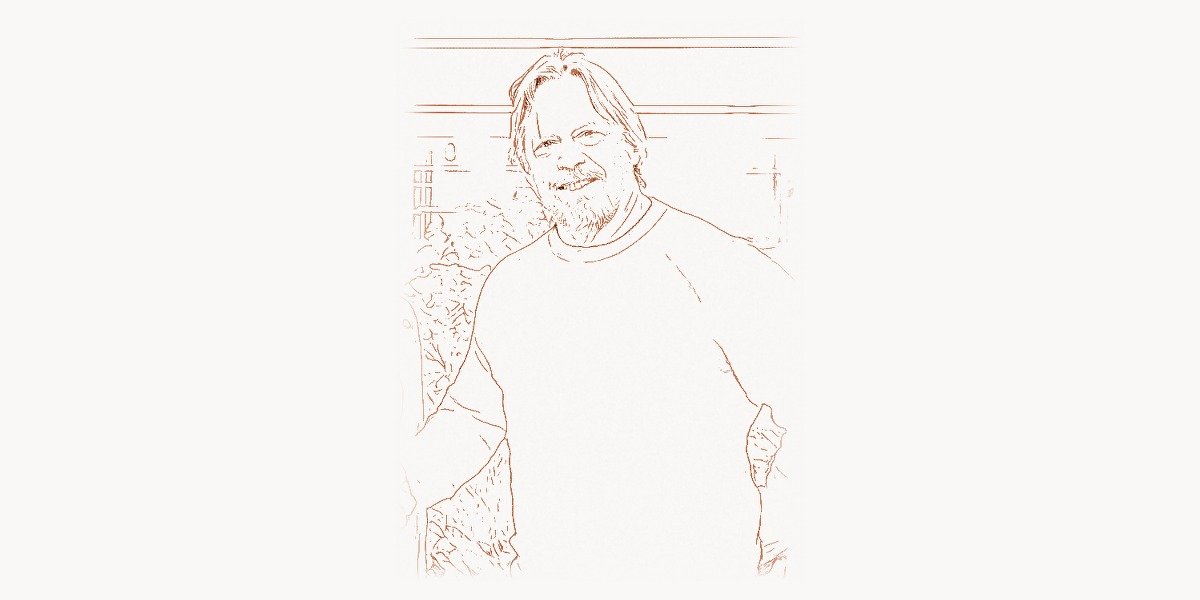

In the world of semiconductor design, one name surfaces again and again across the most important processor breakthroughs of the past three decades: Jim Keller. He is the engineer who designed the AMD K8 architecture that first made 64-bit computing accessible, then returned to AMD fifteen years later to architect Zen — the chip family that rescued the company from near-bankruptcy and broke Intel’s decade-long stranglehold on the server and desktop markets. Between those two AMD stints, he designed the Apple A4 and A5 processors that powered the original iPad and iPhone 4S, led the development of Tesla’s Full Self-Driving chip, and worked on the DEC Alpha — one of the fastest processors ever built at the time. In 2026, as CEO of the AI chip startup Tenstorrent, Keller is attempting to do what he has done his entire career: rethink the fundamental assumptions of processor architecture and deliver a chip that changes the competitive landscape. No other living engineer has left fingerprints on so many transformative processor designs across so many companies.

Early Life and Education

James B. Keller was born in 1958 and grew up in the United States during a period when the semiconductor industry was still in its infancy. He studied electrical engineering at Penn State University, earning his bachelor’s degree, and later completed a master’s degree in computer science. His academic background bridged the gap between hardware and software — a combination that would prove essential throughout his career, as the most impactful processor designs require deep understanding of both the silicon and the code that runs on it.

Keller entered the chip industry in the early 1980s, joining Digital Equipment Corporation (DEC), where he would work on the Alpha processor — a project that shaped his philosophy of computer architecture for decades to come. DEC was one of the great technology companies of its era, and the Alpha team attracted some of the most talented chip designers in the world. Working alongside engineers like Dirk Meyer (who later became AMD’s CEO), Keller absorbed a design culture that prioritized raw performance, elegant microarchitecture, and willingness to challenge established conventions.

The Zen Architecture Breakthrough

Technical Innovation

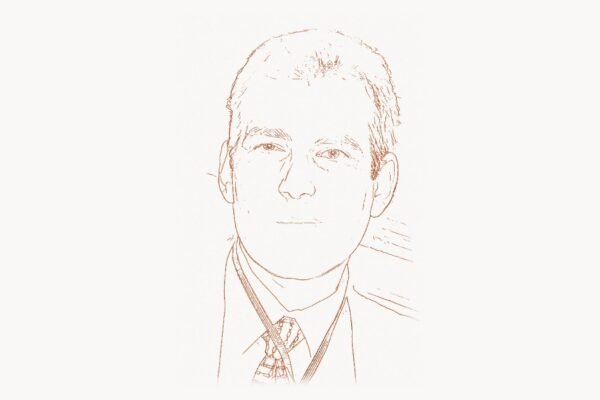

When Jim Keller returned to AMD in August 2012, the company was in crisis. Its Bulldozer architecture, launched in 2011, had been a commercial and technical disaster — it consumed excessive power while delivering single-threaded performance far below Intel’s competing designs. AMD’s stock price had fallen below $2, analysts were openly questioning whether the company would survive, and its server market share had collapsed to single digits. Keller was brought in to lead the design of a completely new architecture from the ground up: Zen.

The Zen architecture represented a radical departure from Bulldozer’s approach. Where Bulldozer had used a “cluster-based multithreading” design that shared execution resources between two threads (resulting in each thread getting significantly less than a full core’s worth of resources), Zen returned to a conventional simultaneous multithreading (SMT) approach with full, independent cores — each with its own dedicated execution units, scheduler, and L1/L2 cache. Keller’s design philosophy was straightforward: build a clean, efficient core with high instructions-per-clock (IPC) performance, then scale it across multiple cores and chiplets.

The technical details of Zen were impressive. Each core featured a micro-op cache that could deliver up to 6 operations per cycle, a 6-wide dispatch front end, 4 integer ALUs, 2 AGUs (address generation units), and 4 floating-point/SIMD pipes. The branch predictor used a neural network-inspired design (a perceptron-based predictor combined with hashed perceptron and BTB) that achieved prediction accuracy exceeding 95% on most workloads. The out-of-order execution window was expanded to 192 entries in the reorder buffer (ROB), compared to Bulldozer’s 128. These changes collectively delivered a 52% IPC improvement over Bulldozer — an almost unprecedented single-generation leap in the x86 world, where 5-10% annual IPC gains were considered normal.

One of the most innovative aspects of Zen was its “Infinity Fabric” interconnect, a scalable communication bus based on HyperTransport technology that allowed AMD to build multi-die and multi-chiplet designs efficiently. This fabric enabled AMD to compose different numbers of CPU core complexes (CCXs), I/O dies, and memory controllers into products ranging from 4-core desktop chips to 64-core server processors — all from the same basic building blocks. This chiplet approach, which Keller’s team designed from the start, gave AMD a manufacturing and economic advantage: they could use smaller, higher-yielding dies and combine them, rather than building monolithic chips where a single defect ruins the entire large die.

To understand how the Zen pipeline processes instructions, consider a simplified view of the decode and dispatch stage — the part of the CPU that translates x86 instructions into internal micro-operations:

/* Simplified model of Zen's decode stage concept.

Real hardware implements this in transistor logic,

but the algorithmic idea can be expressed in C. */

typedef struct {

uint8_t opcode;

uint8_t prefix;

uint8_t modrm;

uint16_t immediate;

} x86_instruction_t;

typedef struct {

uint8_t uop_type; /* ALU, LOAD, STORE, BRANCH */

uint8_t src_reg[3];

uint8_t dst_reg;

uint16_t immediate;

uint8_t execution_port;

} micro_op_t;

/* Zen decodes up to 4 x86 instructions per cycle,

producing up to 6 micro-ops via the micro-op cache */

int decode_cycle(x86_instruction_t *inst_buf, int count,

micro_op_t *uop_buf) {

int uop_count = 0;

for (int i = 0; i < count && i < 4; i++) {

/* Simple instructions map 1:1 to micro-ops */

if (is_simple_op(inst_buf[i].opcode)) {

uop_buf[uop_count++] = translate_simple(inst_buf[i]);

}

/* Complex instructions (e.g., read-modify-write)

decompose into multiple micro-ops */

else {

uop_count += translate_complex(inst_buf[i],

&uop_buf[uop_count]);

}

}

return uop_count; /* Up to 6 uops dispatched */

}Why It Mattered

The impact of Zen cannot be overstated. When the first Zen-based processors (Ryzen) launched in March 2017, they delivered performance competitive with Intel's best desktop chips at significantly lower prices. The server variant (EPYC) was even more disruptive — a single 32-core EPYC chip could match or exceed dual Intel Xeon configurations that cost two to three times as much. Within five years, AMD's server market share climbed from under 1% to over 30%, and its stock price rose from under $2 to over $150. Companies like Lisa Su, who became AMD's CEO in 2014, executed brilliantly on the business side — but it was Keller's Zen architecture that gave her a product worth selling.

The Zen architecture also restored competitive pressure to the entire CPU industry. Intel, which had grown complacent during its years of dominance, was forced to accelerate its own development — moving to higher core counts, adopting chiplet designs (with its own "Foveros" packaging technology), and ultimately bringing in new leadership to overhaul its manufacturing process. Gordon Moore's observation about transistor density may describe a trend, but it takes engineers like Keller to turn those additional transistors into actual performance gains. The ripple effects of Zen reached consumers, cloud providers, and the entire server ecosystem — Amazon AWS, Microsoft Azure, and Google Cloud all adopted EPYC processors for their data centers, and competitive pricing benefited every customer.

It is worth noting that Keller left AMD in September 2015, before Zen shipped — a pattern that recurs throughout his career. He designs the architecture, sets the direction, and moves on to the next challenge. The Zen team continued executing under the leadership of Mike Clark and others, refining the design through Zen 2, Zen 3, Zen 4, and Zen 5 iterations that continued to deliver IPC and efficiency improvements. But the foundational architecture — the core design philosophy, the chiplet approach, the Infinity Fabric — was Keller's work.

Other Major Contributions

DEC Alpha: The Speed Demon

Keller's career began at Digital Equipment Corporation in the 1980s, where he worked on the Alpha processor. The Alpha 21264 (EV6), which Keller contributed to, was one of the fastest processors of its era — it was the first microprocessor to exceed 1 GHz (in 1999) and featured an aggressive out-of-order execution design that influenced subsequent processor architectures across the industry. The Alpha's design philosophy of pursuing maximum clock frequency through deep pipelines and aggressive speculation shaped Keller's understanding of what was possible in processor design. When DEC was acquired by Compaq in 1998, many Alpha engineers — including Keller — dispersed across the industry, carrying the Alpha team's design expertise to AMD, Intel, Apple, and other companies. The Alpha team's diaspora is one of the most consequential talent migrations in semiconductor history.

Apple A4 and A5: ARM Goes Premium

After his first stint at AMD (where he led the K8/Athlon 64 architecture — the first x86 processor to implement 64-bit extensions), Keller joined P.A. Semi, a startup designing low-power, high-performance PowerPC processors. Apple acquired P.A. Semi in 2008 for $278 million, and Keller became part of Apple's nascent chip design team. He played a central role in designing the Apple A4 processor — the custom ARM-based chip that powered the original iPad (2010) and iPhone 4. He also contributed to the A5, which powered the iPad 2 and iPhone 4S.

These chips were significant because they marked Apple's transition from using off-the-shelf ARM processors (designed by Sophie Wilson and her colleagues at ARM) to designing its own custom cores around the ARM instruction set. The A4 and A5 demonstrated that a vertically integrated approach — where the company designing the software also designs the chip — could deliver superior performance and power efficiency. This strategy, which Keller helped establish, ultimately led to Apple's M-series chips for Mac computers, completing Apple's transition away from Intel processors. The architectural DNA of every Apple Silicon chip traces back to the team and approach that Keller helped build.

Tesla Full Self-Driving Chip

In January 2016, Keller joined Tesla as vice president of Autopilot Hardware Engineering. His mission: design a custom chip that could replace the NVIDIA Drive PX 2 hardware that Tesla was using for its Autopilot system. Tesla needed a chip optimized specifically for neural network inference in self-driving applications — something that could process camera data from eight cameras simultaneously, run the neural networks in real-time, and do it all within the power and thermal constraints of a vehicle.

The resulting chip, known as the Tesla FSD (Full Self-Driving) computer or HW3, was announced in April 2019. It contained two custom neural network accelerators, each capable of 36 TOPS (trillion operations per second), along with a 12-core ARM CPU cluster and a GPU. The total system delivered 144 TOPS while consuming only 72 watts — a dramatic improvement over the NVIDIA solution it replaced, which delivered roughly 20 TOPS at similar power levels. Tesla was able to produce these chips at an estimated cost of $190 per unit, far less than the NVIDIA hardware.

The FSD chip was significant for several reasons. It proved that a company outside the traditional semiconductor industry could design a world-class custom chip. It demonstrated that domain-specific architectures — chips designed for a specific workload rather than general-purpose computing — could deliver order-of-magnitude improvements in performance per watt. And it inspired other companies, from Google (with its TPU) to Amazon (with its Graviton and Inferentia chips), to pursue custom silicon for their specific workloads. Keller's ability to rapidly build a chip team and deliver a production chip in approximately three years was remarkable even by industry standards. The work intersected with broader trends in AI hardware that companies like NVIDIA under Jensen Huang were also pursuing, but from the perspective of the customer rather than the GPU vendor.

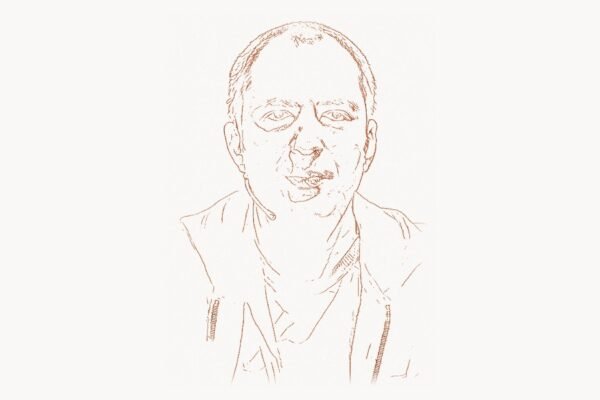

Tenstorrent: The RISC-V Bet

After brief stints at Intel (2018-2020, where he worked on process technology and chip architecture) and a period of advising various companies, Keller became CEO of Tenstorrent in 2023. Tenstorrent is an AI chip startup that has made two bold bets: using the open-source RISC-V instruction set architecture (based on the work of John Hennessy and David Patterson at Berkeley) instead of ARM or x86, and designing a dataflow-based architecture for AI inference and training that fundamentally differs from the GPU-centric approach.

Keller's argument for RISC-V is characteristically direct: the instruction set architecture should be open and free, just as Linux freed operating systems from proprietary control. He sees the future of computing as heterogeneous — systems combining general-purpose CPU cores with specialized AI accelerators, all connected by high-bandwidth interconnects. Tenstorrent's architecture reflects this vision, with RISC-V cores handling general computation while dedicated tensor processing units handle the matrix math that dominates AI workloads. Whether Tenstorrent can compete against NVIDIA's entrenched ecosystem remains one of the most interesting questions in the semiconductor industry.

Design Philosophy

Key Principles

Jim Keller's engineering philosophy can be distilled into several principles that recur across his four decades of chip design. First, simplicity scales — Keller consistently argues that clean, simple designs outperform complicated ones because they can be more easily optimized, debugged, and manufactured. The Zen architecture succeeded partly because it returned to a straightforward core design after Bulldozer's over-engineered complexity. In interviews, Keller has said that the best architectures are the ones where every transistor is doing useful work, not managing the complexity of the design itself.

Second, the right abstraction boundaries matter more than raw transistor count. Keller's chiplet approach in Zen, the domain-specific accelerator design in the Tesla FSD chip, and Tenstorrent's separation of RISC-V cores from tensor units all reflect a belief that dividing a system at the right boundaries enables each component to be optimized independently. This is analogous to good software architecture — and indeed, Keller often draws parallels between chip design and software design, noting that both disciplines benefit from modularity and clean interfaces.

Third, Moore's Law is not dead, but it requires architectural innovation to exploit. Keller has been one of the most vocal advocates against the "Moore's Law is dead" narrative. He argues that while frequency scaling has slowed, the continued increase in transistor density provides enormous opportunity — but only if architects find new ways to use those transistors effectively. Specialized accelerators, chiplet designs, and novel memory hierarchies are all ways to convert additional transistors into real performance, even when clock speeds cannot increase. This perspective aligns with the broader industry trend toward heterogeneous computing, where different types of processing units — CPUs, GPUs, neural network accelerators, signal processors — work together in a single system.

In assembly, the elegance Keller prizes in hardware design mirrors the elegance of a well-optimized instruction sequence. Consider this x86-64 assembly routine for a tight vector dot product — the kind of inner loop that Zen's execution units were specifically designed to accelerate:

; x86-64 AVX2 dot product: two 256-element float arrays

; Zen's 4 FP pipes can execute multiple vfmadd per cycle

; rdi = float *a, rsi = float *b, ecx = 256

dot_product:

vxorps ymm0, ymm0, ymm0 ; accumulator = 0

shr ecx, 3 ; count /= 8 (process 8 floats per iter)

.loop:

vmovups ymm1, [rdi] ; load 8 floats from array a

vfmadd231ps ymm0, ymm1, [rsi] ; ymm0 += ymm1 * b[i..i+7]

add rdi, 32 ; advance pointer by 8 floats

add rsi, 32

dec ecx

jnz .loop

; horizontal sum of ymm0 (8 floats -> 1 float)

vextractf128 xmm1, ymm0, 1 ; upper 128 bits

vaddps xmm0, xmm0, xmm1 ; add upper + lower

vhaddps xmm0, xmm0, xmm0 ; horizontal add

vhaddps xmm0, xmm0, xmm0 ; final horizontal add

ret ; result in xmm0[0]This kind of loop — tight, vectorized, minimizing memory stalls — is exactly what Zen's wide execution units and deep out-of-order buffers were designed to handle. Keller's architectures do not just add transistors; they ensure those transistors directly accelerate the workloads that matter. For teams managing complex hardware projects at this scale, tools like Taskee can help coordinate the thousands of design tasks and verification milestones that modern chip development requires.

Legacy and Modern Relevance

Jim Keller's legacy is unusual in the tech industry because it spans so many companies and so many different product categories. Most great engineers are associated with a single company or a single product line — Gordon Moore with Intel, Jensen Huang with NVIDIA, Sophie Wilson with ARM. Keller's fingerprints are on DEC Alpha, AMD K8, AMD Zen, Apple A4/A5, Tesla FSD, and now Tenstorrent's RISC-V AI chips. This breadth reflects both his restless drive to tackle new problems and the universal nature of his expertise — the principles of good processor design apply whether you are building a server chip, a mobile SoC, an autonomous driving computer, or an AI accelerator.

In 2026, the semiconductor industry is more important than it has been at any point since the invention of the integrated circuit. AI workloads are driving unprecedented demand for compute, geopolitical competition over chip manufacturing has made semiconductors a matter of national security, and every major technology company — from Apple to Amazon to Tesla — is either designing custom chips or considering it. Jim Keller is at the center of this moment, leading Tenstorrent's challenge to the established order. Regardless of whether Tenstorrent succeeds commercially, Keller has already earned his place as one of the most impactful processor architects in computing history — the engineer who revived AMD twice, helped Apple build its silicon empire, gave Tesla its self-driving brain, and never stopped pushing the boundaries of what a chip can do.

For organizations navigating the complex landscape of modern technology — from semiconductor design to software development — having a clear strategic framework is essential. Agencies like Toimi help companies develop digital strategies that account for the rapid pace of hardware and software evolution that engineers like Keller continue to drive.

Key Facts

- Full name: James B. Keller

- Born: 1958, United States

- Education: B.S. Electrical Engineering (Penn State), M.S. Computer Science

- Known for: AMD K8 (Athlon 64), AMD Zen (Ryzen/EPYC), Apple A4/A5, Tesla FSD chip, DEC Alpha contributions

- Key companies: DEC (1980s–1998), AMD (1998–2008, 2012–2015), P.A. Semi/Apple (2008–2012), Tesla (2016–2018), Intel (2018–2020), Tenstorrent (2023–present)

- Current role: CEO of Tenstorrent (RISC-V AI chip startup)

- Notable achievement: Zen architecture delivered 52% IPC improvement over predecessor, rescuing AMD from near-bankruptcy

- Architecture philosophy: Simplicity scales — clean designs outperform complicated ones

Frequently Asked Questions

Who is Jim Keller and why is he called the greatest chip architect alive?

Jim Keller is an American electrical engineer and processor architect who has designed or led the design of some of the most important computer processors of the past three decades. He earned the informal title of "greatest chip architect alive" because of the unprecedented breadth and impact of his work: the AMD K8 (the first 64-bit x86 processor), the AMD Zen architecture (which saved AMD from potential bankruptcy and broke Intel's monopoly), the Apple A4/A5 processors (which launched Apple's custom silicon strategy), and the Tesla FSD chip (which demonstrated that a non-semiconductor company could design a world-class AI chip). No other living engineer has been the lead architect on transformative processor designs at so many different companies.

What was Jim Keller's role in the AMD Zen architecture?

Keller joined AMD in August 2012 as corporate vice president and chief architect of microprocessor cores. He led the ground-up design of the Zen architecture, which replaced the failed Bulldozer design with a clean, efficient core featuring simultaneous multithreading, a wide execution engine, and a revolutionary chiplet-based approach using AMD's Infinity Fabric interconnect. Zen delivered a 52% improvement in instructions per clock over Bulldozer. Keller departed AMD in September 2015, before Zen-based products shipped in 2017, but the architectural foundation he laid has driven every subsequent generation of AMD processors through Zen 5 and beyond. Working alongside CEO Lisa Su, Keller's Zen design was the technical catalyst for AMD's dramatic market resurgence.

What is Jim Keller doing now at Tenstorrent?

As of 2026, Keller serves as CEO of Tenstorrent, an AI chip startup based in Toronto. Tenstorrent is developing AI processors based on the open-source RISC-V instruction set architecture, combined with a custom dataflow-based tensor processing architecture designed for machine learning training and inference. Keller's vision at Tenstorrent is to challenge NVIDIA's dominance in AI hardware by offering an open, licensable chip architecture that companies can customize for their specific AI workloads — similar to how ARM licenses CPU designs, but built on the fully open RISC-V standard. The company has attracted significant investment and is positioning itself as a key player in the next generation of AI computing infrastructure, building on the modern development tools and open-source ecosystems that power today's hardware design workflows.